PCB设计-EMC设计规范

2020-03-19 loonlog 4433 2

本文目录

PCB设计过程中,最令人头疼的问题,也是最玄的问题,更是决定性能、成败的问题,就是EMC的问题了;EMC设计的不好,有可能干扰别人不能工作,也可能受别人或者受自己的干扰,自己不能好好工作,即使正常工作了,不能满足相关标准,产品就不能通过认证,就不能上市,也是很尴尬的;本人在军工企业干过,EMC过不了,会受很多相关单位的嘲笑,鸭梨山大。

以下规则,也是来自网络,站在巨人的肩膀上,共同学习,遇到新情况,继续更新。

充分考虑器件的摆放和方向

避免时钟谐波的重叠,将所有时钟的谐波分量以表列出

时钟环路越小越好!对时钟信号要格外注意!

尽可能采用包括电源/地平面的多层板结构

所有高速信号线必须有相邻层作为参考平面

信号层和参考平面层距离尽量小(<10mils)

信号频率超过25MHz的PCB应有2个(或更多)的GND层

20H原则,电源层边缘相对于邻近的GND层边缘内缩,内缩距离为电源/地平面间距的20倍

尽量让时钟信号在高速层(夹在电源或地平面之间的信号层)上走线

避免狭槽状的地或电源shape

信号线不得跨过分割的电源平面

在时钟驱动器的输出端提供过滤(或串联端接)措施,减小时钟上升/下降沿跳变,减小振铃(端接电阻大小通常33-70欧)

时钟和高速信号线远离IO区域

DIP封装器件至少用两颗同样值的去耦电容;矩形封装器件用四颗去耦电容;高速/功耗/噪声IC旁尽可能多放去耦电容

在大于50MHz的高速板上考虑使用埋容增加去耦效果

板上走线的阻抗控制&适当的端接措施

在阻抗控制的PCB上,信号换层时参考平面不要变化

在非阻抗控制的PCB上,时钟更换参考层时,在不同参考层间增加流通孔/transfer via或缝合电容

信号线长度(英寸单位)大于等于信号的上升/下降时间(纳秒单位)的话,必须对信号串联端接(通常是33欧)

仿真所有信号长度(英寸单位)大于等于信号上升/下降时间(纳秒单位)的信号

在IO区域将逻辑GND和CHASSIS连接一起(通过非常低阻抗的连接…),这很重要!

在时钟和振荡器位置,也提供类似的GND到CHASSIS的连接

可能需要到的额外的GND到CHASSIS的连接

高速的子板(可能包括高速器件和外部连接线)和母版间的GND/CHASSIS连接保证良好,不要仅仅依靠连接器的GND脚互连

对IO信号进行共模抑制,对PCB既定区域内的IO信号线分组

IO处(接口)的滤波电容到CHASSIS网络的阻抗必须很低

DC电源输入位置最好使用共模/差模抑制器件

塑料外壳的产品需要额外的金属参考平面/板

可以的话,在板级对器件采取屏蔽措施

所有的散热片接地

EMC设计建议

1、地平面的设计。低感抗的地回路是PCB设计过程中抑制EMC问题的最有效方法。扩大地平面区域,降低地回路的感抗,可以有效地降低辐射和串扰。

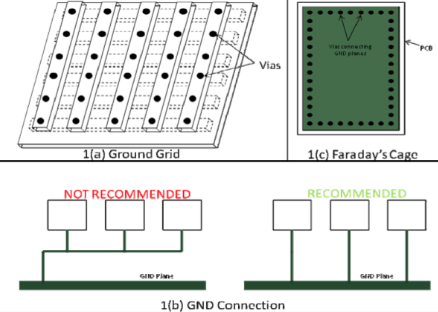

信号的地回路设计有多种方法,较差的方法是将器件随意地接到地网络。这种高感抗的地回路设计会引起不可预期的EMC问题。推荐的方法是用一个完整的地平面为信号回流提供最低阻抗的路径。显然,对于两层PCB,完整地平面是不切实际的。在这种情况下,设计者可以使用地网格的方法,如图1a所示。在这种情况下,回路感抗大小取决于网格间距大小。

信号的回流是非常重要的。更长的回流路径意味着更大的回流路径,由此带来天线效应和向外辐射能量。因此,信号回流应该走最短的路径,直接连到地平面。单点连接所有点,再把它们连到一起接到地平面是不可取的,这样不仅增加电流环路大小,而且增加了地弹的可能性。图1b示意了推荐的器件到地平面的连接方式。

法拉第电笼是另外一个减小EMC问题的办法。法拉第电笼是在PCB外围四周增加一圈地缝合孔,注意电笼外面不走线。如图1c所示,法拉第电笼有效地抑制了PCB到/来自板外的辐射/干扰。在表层推荐用一条宽度为200~400mils的地线将所有GND孔连接;在信号层,推荐用一条宽度为20~40mils的地线将这些GND孔连接,但不建议连线成环路。

2、器件隔离。根据功能,将元器件分组,不同组放在PCB板上的不同位置,如模拟信号、数字信号、电源部分,低速信号和高速信号等。各组信号应在它们各自分配区域内,信号经过不同组之间(从一个子系统到另外一个),应当在边界处增加过滤措施。

3、 叠层设计。多于两层板的设计,应当有一个完整的地平面。在四层板……应当注意,在高速信号层和高速信号线之间应当有GND层。对于两层板,完整的GND平面不现实,可以采用地格点的方式。如果没有单独的电源平面,建议在电源走线下方平行走GND线以保证供电的稳定。

注:GND层相对于电源层和器件层向外延伸20h,屏蔽噪声。/h: 电源和地平面的间距

4、数字电路。处理数字电路的时候尤其要注意时钟信号和高速信号线,这些信号走线尽量短,且走线靠近地平面以保证辐射和串扰在可控范围内。对于这些信号,注意减少使用过孔、避免在PCB边缘走线或靠近连接器。这些信号也应远离电源平面,因为它们可能将噪声耦合到电源平面上去。

对于振荡器的处理,除了用GND隔离外。信号线注意不要平行或走在振荡器下方,与CLK信号保证有足够距离。振荡器与使用时钟的芯片尽量靠近。

注意回流总是沿着阻抗最低路径的。因此,负载回流的GND应与其信号路径尽量近,使电流回路面积最小。

差分对之间P/N线相互靠近,这样可以有效地进行共模抑制。

5、时钟端接。时钟信号线注意阻抗匹配,否则会引起信号反射。如果不对反射信号进行处理,这些信号会被辐射出去。有多种有效的端接方式,包括源端端接、末端端接和AC端接等。

6、模拟电路。模拟信号应远离高速跳变信号,通过GND将这些信号隔离。应用中常用低通滤波器滤除周边模拟信号的高频噪声。另外,模拟地和数字地应当分开。

7、去耦电容。电源上的任何噪声都有可能造成器件工作不正常,一般来说,耦合到电源上的是一些高频的杂讯,可以通过使用去耦电容滤除,去耦电容为高频杂讯提供电源到GND的低阻抗路径。信号回流路径构成电源到地的环状结构,将去耦电容尽量靠近IC管脚摆放,使得回流环面积最小。大面积的回流环路会增加辐射,成为潜在的EMC失效原因。

理论上,电容的电抗值随着频率的上升逐渐接近于零,然而并不存在这样的理想情况,封装和引脚都会增加电容的等效电感值。同时使用多个低ESL电容有助于增强去耦效果。

8、线缆。许多EMC问题是在高速信号通过电缆时,线缆充当天线造成的。理想情况下,电流从一端流入线缆,在另一端无衰减地流出。实际情况是寄生电容和电感的存在会造成辐射,产生EMI问题。通过双绞线抑制感应磁场,可以使耦合保持在低的水平。在使用带状线的时候,注意提供多个GND回路(多GND线)。对于高频信号,应在线缆两端都提供GND屏蔽线。

9、串扰。串扰存在于PCB上任意两条走线之间,串扰的大小与互感、互容、信号的边缘速率,以及走线的阻抗有关。在数字系统中,由互感引起的串扰一般会大于由互容引起的串扰。通过增加信号线之间的距离,或减小信号线与GND的距离都可以减小信号线之间的互感。

10、屏蔽。屏蔽不是降低EMC的电子学方法,而是一种机构手段。金属性(导体或磁性材料)外壳可以用来屏蔽对系统外的EMI。根据实际要求,屏蔽可以是针对部分或者整体的。屏蔽腔相当于一个封闭的接地容器,可以有效地吸收和反射辐射从而降低环状天线的大小。同样地,屏蔽也可以是不同部分间的隔离,衰减从一部分到另一部分辐射的能量。屏蔽通过衰减辐射波的E参数和H参数达到降低EMI的作用!

引用:

http://www.wangdali.net/emc10/

https://www.cypress.com/file/106951/download

http://www.hottconsultants.com/pdf_files/pcb_guide.pdf

推荐网站:

http://www.hottconsultants.com/

Allegro , AD , 电路 , PCB , Altium designer , 电子电路

http://loonlog.com/2020/3/19/pcb-emc/

评论列表,共 2 条评论

回复

技术员 哈哈!!

回复

就是个苦逼打工的